Table of Contents

ToggleIntroduction

Definition of Chip Packaging

Chip packaging is the process of enclosing and protecting an integrated circuit (IC) or semiconductor chip, providing it with a secure and durable package. It involves assembling the chip into a protective casing, establishing electrical connections, and facilitating the dissipation of heat generated during operation.

Importance of Chip Packaging

Chip packaging plays a crucial role in the semiconductor industry, as it ensures the proper functioning, reliability, and durability of electronic devices. It protects the delicate chip from external factors such as moisture, dust, and mechanical stress, while also enabling efficient electrical connections and thermal management.

Types of Chip Packaging Methods

Leadframe Packaging

Leadframe packaging is one of the most common and traditional methods of chip packaging. It involves mounting the chip on a metal leadframe, which provides electrical connections and support.

Plastic Dual In-line Package (PDIP)

The Plastic Dual In-line Package (PDIP) is a through-hole package with two parallel rows of leads. It is widely used in various electronic devices, such as computers, consumer electronics, and industrial applications.

Small Outline Integrated Circuit (SOIC)

The Small Outline Integrated Circuit (SOIC) is a surface-mount package that features gull-wing shaped leads. It offers a compact size and is commonly used in smartphones, laptops, and other portable electronics.

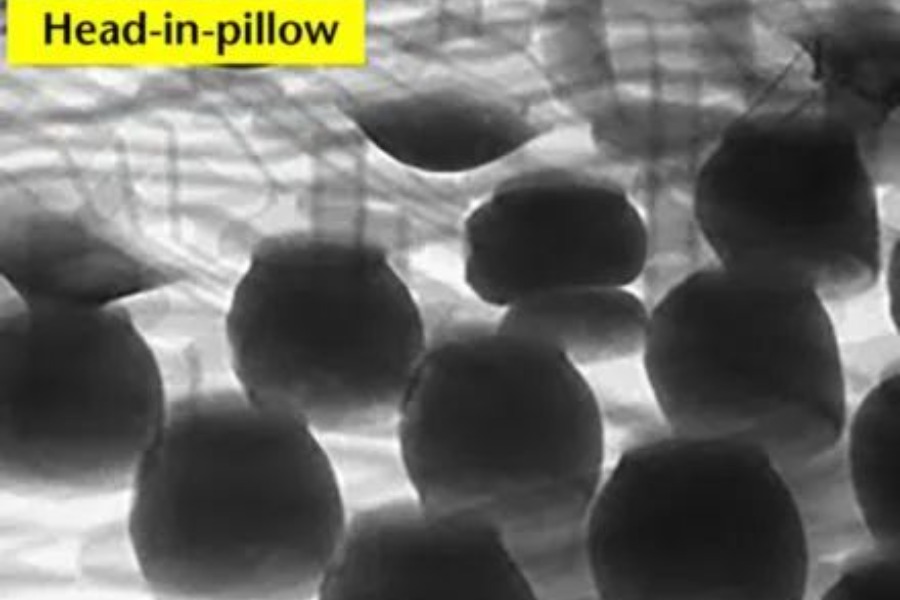

Ball Grid Array (BGA)

The Ball Grid Array (BGA) is a surface-mount packaging technique that utilizes an array of solder balls as electrical connections. It offers high pin counts and is suitable for high-density and high-performance applications.

Plastic Ball Grid Array (PBGA)

The Plastic Ball Grid Array (PBGA) is a cost-effective variant of the BGA package, featuring a plastic substrate and solder balls for electrical connections. It is widely used in consumer electronics and computer peripherals.

Ceramic Ball Grid Array (CBGA)

The Ceramic Ball Grid Array (CBGA) is a high-performance and reliable package suitable for harsh environments. It features a ceramic substrate and is commonly used in military, aerospace, and industrial applications.

Flip Chip

Flip chip packaging is a technique where the chip is mounted face-down onto the substrate or package carrier. This method provides a compact package size and improved electrical performance due to the shorter connections between the chip and the substrate.

Wafer Level Packaging (WLP)

Wafer Level Packaging (WLP) is an advanced packaging method that involves packaging the chips while they are still in the wafer form, before they are singulated (cut into individual chips).

Fan-Out Wafer Level Packaging (FOWLP)

Fan-Out Wafer Level Packaging (FOWLP) is a variant of WLP where the package is larger than the chip itself. This allows for increased input/output (I/O) density and higher integration.

Fan-In Wafer Level Packaging (FIWLP)

Fan-In Wafer Level Packaging (FIWLP) is another type of WLP where the package size is smaller or equal to the chip size. It offers a compact form factor and is suitable for mobile and wearable devices.

Factors Influencing Chip Packaging Selection

Size and Form Factor

The size and form factor of the electronic device are crucial factors in selecting the appropriate chip packaging method. Compact packages like BGA and WLP are preferred for portable and space-constrained applications, while larger packages like PDIP may be suitable for desktop or industrial applications.

Thermal Management

Effective thermal management is essential for ensuring the reliable operation of chips. Packaging methods that offer good heat dissipation capabilities, such as ceramic packages or packages with heat spreaders, are preferred for high-power and high-performance applications.

Electrical Performance

The electrical performance requirements, including signal integrity, power delivery, and electromagnetic compatibility (EMC), influence the choice of chip packaging. Packages with shorter electrical paths and better shielding capabilities, like flip chip or BGA, offer superior electrical performance.

Cost

Cost is a significant factor, especially in consumer electronics and high-volume applications. Plastic packages like PDIP, SOIC, and PBGA are generally more cost-effective compared to ceramic packages or advanced packaging techniques like WLP.

Application Requirements

The specific requirements of the target application, such as operating environment, reliability standards, and performance specifications, play a crucial role in selecting the appropriate chip packaging method.

Packaging Process and Materials

Die Preparation

The packaging process begins with the preparation of the semiconductor die (chip). This involves wafer processing, testing, and singulation (cutting the wafer into individual chips).

Substrate or Leadframe

The substrate or leadframe provides the base for the chip and establishes electrical connections. Common materials used include plastic, ceramic, and metals like copper or aluminum.

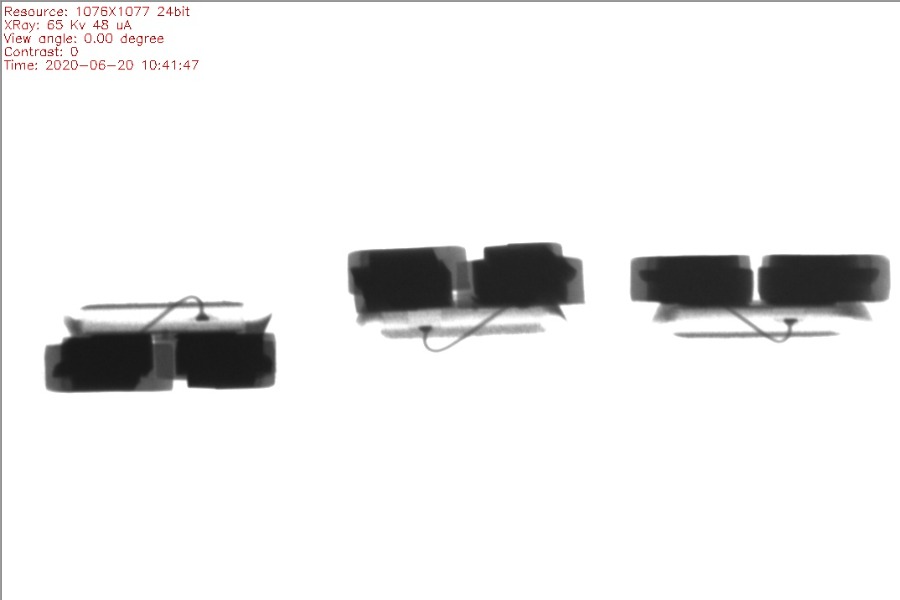

Bonding

Bonding is the process of creating electrical connections between the chip and the substrate or leadframe. This can be done through wire bonding, flip chip bonding, or other techniques.

Encapsulation

Encapsulation involves enclosing the chip and its electrical connections within a protective material, such as plastic or ceramic. This step protects the chip from external factors and provides structural support.

Testing and Marking

After encapsulation, the packaged chip undergoes thorough testing to ensure its functionality and reliability. It is then marked with identification information, such as part numbers or manufacturer logos.

Trends and Future of Chip Packaging

Miniaturization and Increased Integration

The trend towards miniaturization and increased integration is driving the development of smaller and more compact chip packaging techniques. This includes the adoption of advanced packaging methods like WLP and 3D/2.5D packaging.

Advanced Materials

New and advanced materials are being explored for chip packaging to improve performance, reliability, and thermal management. These include high-performance organic substrates, liquid cooling solutions, and advanced encapsulation materials.

3D and 2.5D Packaging

3D and 2.5D packaging technologies, which involve stacking multiple chips or integrating chips and passive components into a single package, are gaining traction. These techniques offer higher integration, improved performance, and reduced form factors.

Conclusion

The packaging methods of chips play a vital role in the semiconductor industry, ensuring the protection, functionality, and reliability of electronic devices. From traditional leadframe packages to advanced techniques like WLP and 3D packaging, the selection of the appropriate packaging method depends on various factors, including size, thermal management, electrical performance, cost, and application requirements.

As technology continues to evolve, chip packaging methods will need to adapt to meet the demands for higher integration, better performance, and more compact form factors. The future of chip packaging lies in the development of innovative materials, advanced packaging techniques, and ongoing miniaturization efforts to support the ever-growing needs of the electronics industry.

FAQs

Q1: What is the difference between fan-out and fan-in wafer level packaging?

A1: In fan-out wafer level packaging (FOWLP), the package size is larger than the chip itself, allowing for increased input/output (I/O) density and higher integration. On the other hand, fan-in.

Q2: What are the advantages of ball grid array (BGA) packaging?

A2: Ball grid array (BGA) packaging offers several advantages, including:

- High pin count and high density: BGA packages can accommodate a large number of input/output connections, making them suitable for high-performance and high-density applications.

- Improved electrical performance: The shorter electrical paths in BGA packages result in better signal integrity and reduced noise, enabling higher operating frequencies.

- Enhanced thermal management: The array of solder balls provides a larger surface area for heat dissipation, improving thermal performance.

- Surface mount compatibility: BGA packages are designed for surface mount technology, enabling automated assembly processes and reducing board space requirements.

Q3: What is the purpose of encapsulation in chip packaging?

A3: Encapsulation is a crucial step in chip packaging that serves several purposes:

- Protection: It shields the delicate chip and its electrical connections from external factors like moisture, dust, and mechanical stress, ensuring reliability and prolonging the chip’s lifespan.

- Structural support: The encapsulation material, such as plastic or ceramic, provides structural integrity and robustness to the package, preventing damage during handling and operation.

- Thermal management: Some encapsulation materials possess good thermal conductivity, facilitating heat dissipation from the chip.

- Electrical insulation: The encapsulation material electrically insulates the chip and its connections from external interference or short circuits.

Q4: What are the key considerations when selecting a chip packaging method?

A4: The selection of a chip packaging method depends on several key considerations:

- Size and form factor requirements of the end application

- Thermal management needs based on the chip’s power dissipation

- Electrical performance requirements, such as signal integrity and power delivery

- Cost constraints, especially for high-volume consumer applications

- Specific application requirements, such as operating environment and reliability standards

- Future scalability and integration needs for the product or system

Q5: What are the emerging trends in chip packaging for the future?

A5: Some of the emerging trends in chip packaging for the future include:

- Continued miniaturization and increased integration through advanced packaging techniques like fan-out wafer level packaging (FOWLP) and 3D/2.5D packaging.

- Adoption of new and advanced materials for substrates, encapsulation, and thermal management solutions to improve performance and reliability.

- Development of embedding technologies that integrate passive components like capacitors and resistors into the package itself, enabling further miniaturization.

- Exploration of heterogeneous integration, where different types of chips (e.g., logic, memory, analog) are integrated into a single package for improved functionality and performance.

- Increased focus on thermal management solutions, such as liquid cooling and integrated heat spreaders, to address the thermal challenges of high-performance and power-dense packages.