Inhoudsopgave

SchakelaarInvoering

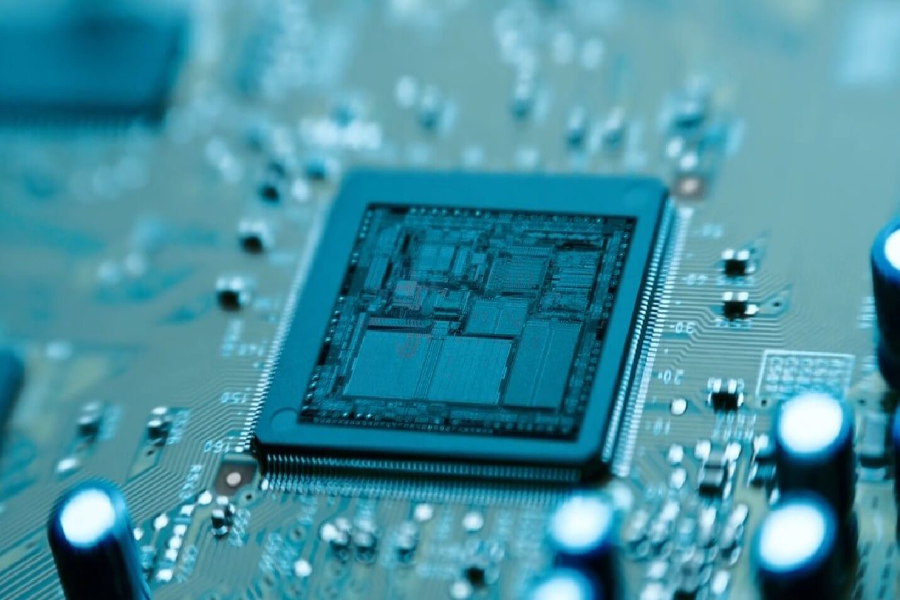

Definitie van chipverpakking

Chipverpakking is het proces van het omhullen en beschermen van een geïntegreerd circuit (IC) of halfgeleiderchip, waarbij het voorzien wordt van een veilige en duurzame verpakking. Het houdt in dat de chip in een beschermend omhulsel wordt geassembleerd, elektrische verbindingen worden gemaakt en de warmte die vrijkomt tijdens het gebruik wordt afgevoerd.

Het belang van chipverpakking

Chipverpakking speelt een cruciale rol in de halfgeleiderindustrie, omdat het zorgt voor de goede werking, betrouwbaarheid en duurzaamheid van elektronische apparaten. Het beschermt de kwetsbare chip tegen externe factoren zoals vocht, stof en mechanische stress, terwijl het ook efficiënte elektrische verbindingen en thermisch beheer mogelijk maakt.

Soorten chipverpakkingsmethoden

Leadframe verpakking

Leadframe verpakking is een van de meest voorkomende en traditionele methodes om chips te verpakken. Hierbij wordt de chip op een metalen leadframe gemonteerd, dat elektrische verbindingen en ondersteuning biedt.

Plastic dubbel-in-lijn pakket (PDIP)

Het Plastic Dual In-line Package (PDIP) is een doorvoergatverpakking met twee parallelle rijen aansluitdraden. Het wordt veel gebruikt in verschillende elektronische apparaten, zoals computers, consumentenelektronica en industriële toepassingen.

SOIC (Small Outline Integrated Circuit)

De SOIC (Small Outline Integrated Circuit) is een opbouwpakket met vleugelvormige aansluitdraden. Hij heeft een compact formaat en wordt vaak gebruikt in smartphones, laptops en andere draagbare elektronica.

BGA (Ball Grid Array)

De Ball Grid Array (BGA) is een aan de oppervlakte gemonteerde verpakkingstechniek die gebruik maakt van een reeks soldeerbolletjes als elektrische verbindingen. Het biedt een hoog aantal pinnen en is geschikt voor toepassingen met een hoge dichtheid en hoge prestaties.

Kunststof balraster (PBGA)

De Kunststof bal rooster (PBGA) is een kosteneffectieve variant van de BGA-pakket, met een plastic substraat en soldeerbolletjes voor elektrische verbindingen. Het wordt veel gebruikt in consumentenelektronica en computerrandapparatuur.

CBGA (Ceramic Ball Grid Array)

De Keramisch Kogelraster (CBGA) is een krachtige en betrouwbare verpakking die geschikt is voor ruwe omgevingen. Het heeft een keramisch substraat en wordt vaak gebruikt in militaire, ruimtevaart- en industriële toepassingen.

Flip Chip

Flip chip verpakking is een techniek waarbij de chip met de voorkant naar beneden op het substraat of de verpakkingsdrager wordt gemonteerd. Deze methode zorgt voor een compacte verpakking en betere elektrische prestaties door de kortere verbindingen tussen de chip en het substraat.

Verpakking op waferniveau (WLP)

Verpakking op waferniveau (WLP) is een geavanceerde verpakkingsmethode waarbij de chips worden verpakt terwijl ze nog in wafelvorm zijn, voordat ze worden gesinguleerd (in afzonderlijke chips worden gesneden).

Fan-Out Wafer Level Packaging (FOWLP)

Fan-Out Wafer Level Packaging (FOWLP) is een variant van WLP waarbij de verpakking groter is dan de chip zelf. Dit zorgt voor een hogere input/output (I/O) dichtheid en hogere integratie.

Fan-In Wafer Level Packaging (FIWLP)

Fan-In Wafer Level Packaging (FIWLP) is een ander type WLP waarbij de verpakkingsgrootte kleiner of gelijk is aan de chipgrootte. Het biedt een compacte vormfactor en is geschikt voor mobiele en draagbare apparaten.

Factoren die de keuze van de chipverpakking beïnvloeden

Grootte en vormfactor

De grootte en vormfactor van het elektronische apparaat zijn cruciale factoren bij het kiezen van de juiste chipverpakkingsmethode. Compacte verpakkingen zoals BGA en WLP hebben de voorkeur voor draagbare en ruimtebesparende toepassingen, terwijl grotere verpakkingen zoals PDIP geschikt kunnen zijn voor desktop- of industriële toepassingen.

Thermisch beheer

Effectief thermisch beheer is essentieel voor een betrouwbare werking van chips. Verpakkingsmethodes die een goede warmteafvoer bieden, zoals keramische pakketten of pakketten met warmtespreiders, genieten de voorkeur voor toepassingen met een hoog vermogen en hoge prestaties.

Elektrische prestaties

De vereisten voor elektrische prestaties, waaronder signaalintegriteit, stroomtoevoer en elektromagnetische compatibiliteit (EMC), beïnvloeden de keuze van de chipverpakking. Verpakkingen met kortere elektrische paden en betere afscherming, zoals flip chip of BGA, bieden superieure elektrische prestaties.

Kosten

Kosten zijn een belangrijke factor, vooral in consumentenelektronica en toepassingen met hoge volumes. Plastic verpakkingen zoals PDIP, SOIC en PBGA zijn over het algemeen kosteneffectiever dan keramische verpakkingen of geavanceerde verpakkingstechnieken zoals WLP.

Aanvraagvereisten

De specifieke vereisten van de doeltoepassing, zoals bedrijfsomgeving, betrouwbaarheidsnormen en prestatiespecificaties, spelen een cruciale rol bij de keuze van de juiste chipverpakkingsmethode.

Verpakkingsproces en materialen

Matrijsvoorbereiding

Het verpakkingsproces begint met de voorbereiding van de halfgeleider-die (chip). Dit omvat het verwerken van de wafer, testen en singuleren (de wafer in afzonderlijke chips snijden).

Substraat of loodframe

Het substraat of leadframe vormt de basis voor de chip en zorgt voor de elektrische verbindingen. Veel gebruikte materialen zijn plastic, keramiek en metalen zoals koper of aluminium.

Verbinding

Bonding is het proces waarbij elektrische verbindingen worden gemaakt tussen de chip en het substraat of leadframe. Dit kan gebeuren door middel van wire bonding, flip chip bonding of andere technieken.

Inkapseling

Inkapseling houdt in dat de chip en zijn elektrische verbindingen worden omhuld door een beschermend materiaal, zoals plastic of keramiek. Deze stap beschermt de chip tegen externe factoren en biedt structurele ondersteuning.

Testen en markeren

Na de inkapseling wordt de verpakte chip grondig getest om de functionaliteit en betrouwbaarheid te garanderen. Vervolgens wordt de chip gemarkeerd met identificatie-informatie, zoals onderdeelnummers of logo's van de fabrikant.

Trends en toekomst van chipverpakking

Miniaturisatie en verhoogde integratie

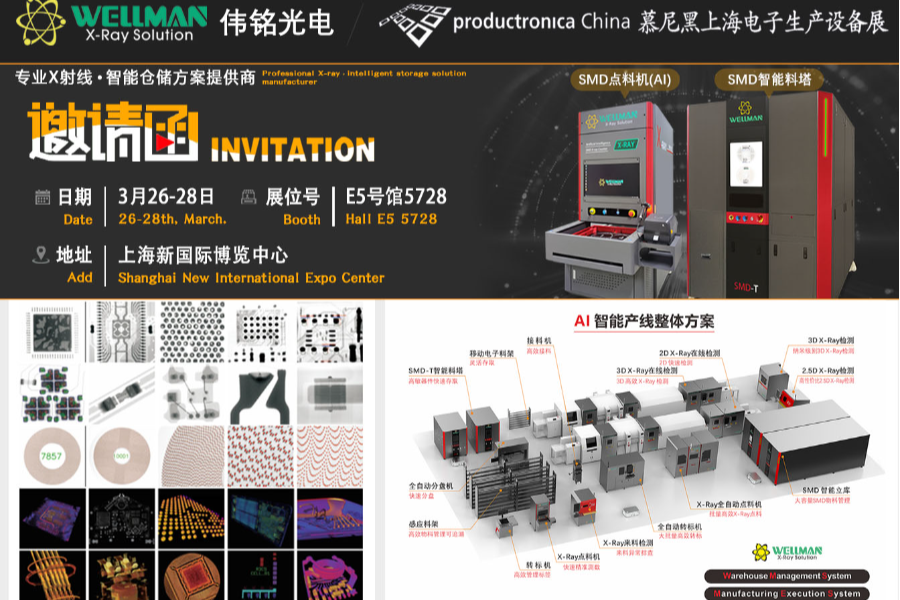

De trend naar miniaturisatie en meer integratie stimuleert de ontwikkeling van kleinere en compactere chipverpakkingstechnieken. Dit omvat de toepassing van geavanceerde verpakkingsmethoden zoals WLP en 3D/2,5D-verpakking.

Geavanceerde Materialen

Nieuwe en geavanceerde materialen worden onderzocht voor chipverpakking om de prestaties, betrouwbaarheid en het thermisch beheer te verbeteren. Hieronder vallen hoogwaardige organische substraten, oplossingen voor vloeistofkoeling en geavanceerde inkapsulatiematerialen.

3D en 2,5D verpakking

3D- en 2,5D-verpakkingstechnologieën, waarbij meerdere chips worden gestapeld of chips en passieve componenten in een enkele verpakking worden geïntegreerd, winnen aan populariteit. Deze technieken bieden meer integratie, betere prestaties en kleinere vormfactoren.

Conclusie

De verpakkingsmethoden van chips spelen een vitale rol in de halfgeleiderindustrie en zorgen voor de bescherming, functionaliteit en betrouwbaarheid van elektronische apparaten. Van traditionele leadframe-pakketten tot geavanceerde technieken zoals WLP en 3D-verpakking, de keuze van de juiste verpakkingsmethode hangt af van verschillende factoren, waaronder grootte, thermisch beheer, elektrische prestaties, kosten en toepassingsvereisten.

Naarmate de technologie zich blijft ontwikkelen, zullen de verpakkingsmethoden voor chips zich moeten aanpassen om te voldoen aan de vraag naar meer integratie, betere prestaties en compactere vormfactoren. De toekomst van chipverpakking ligt in de ontwikkeling van innovatieve materialen, geavanceerde verpakkingstechnieken en voortdurende miniaturisatie om te voldoen aan de steeds groeiende behoeften van de elektronica-industrie.

Veelgestelde vragen

V1: Wat is het verschil tussen fan-out en fan-in verpakking op waferniveau?

A1: Bij fan-out wafer level packaging (FOWLP) is de grootte van de verpakking groter dan de chip zelf, waardoor een grotere input/output (I/O) dichtheid en hogere integratie mogelijk is. Aan de andere kant is fan-in.

V2: Wat zijn de voordelen van ball grid array (BGA) verpakking?

A2: Ball grid array (BGA) verpakkingen bieden verschillende voordelen, waaronder:

- Hoog aantal pinnen en hoge dichtheid: BGA-pakketten kunnen een groot aantal ingangs-/uitgangsverbindingen bevatten, waardoor ze geschikt zijn voor toepassingen met hoge prestaties en hoge dichtheid.

- Verbeterde elektrische prestaties: De kortere elektrische paden in BGA-pakketten resulteren in een betere signaalintegriteit en minder ruis, waardoor hogere werkfrequenties mogelijk zijn.

- Verbeterd thermisch beheer: De reeks soldeerbolletjes biedt een groter oppervlak voor warmteafvoer, waardoor de thermische prestaties verbeteren.

- Compatibel met opbouwmontage: BGA-pakketten zijn ontworpen voor opbouwmontagetechnologie, waardoor geautomatiseerde assemblageprocessen mogelijk zijn en minder printplaatruimte nodig is.

V3: Wat is het doel van inkapseling in chipverpakking?

A3: Inkapseling is een cruciale stap in chipverpakking die verschillende doelen dient:

- Bescherming: Het beschermt de kwetsbare chip en zijn elektrische verbindingen tegen externe factoren zoals vocht, stof en mechanische stress, waardoor de betrouwbaarheid wordt gegarandeerd en de levensduur van de chip wordt verlengd.

- Structurele ondersteuning: Het inkapselingsmateriaal, zoals plastic of keramiek, biedt structurele integriteit en robuustheid aan de verpakking, waardoor schade tijdens hantering en gebruik wordt voorkomen.

- Thermisch beheer: Sommige inkapselingsmaterialen hebben een goede thermische geleiding, waardoor de warmteafvoer van de chip wordt vergemakkelijkt.

- Elektrische isolatie: Het inkapselingsmateriaal isoleert de chip en zijn aansluitingen elektrisch van externe interferentie of kortsluiting.

V4: Wat zijn de belangrijkste overwegingen bij het kiezen van een chipverpakkingsmethode?

A4: De keuze van een chipverpakkingsmethode hangt af van verschillende belangrijke overwegingen:

- Vereisten voor grootte en vormfactor van de eindtoepassing

- Behoefte aan thermisch beheer gebaseerd op de vermogensdissipatie van de chip

- Vereisten voor elektrische prestaties, zoals signaalintegriteit en stroomvoorziening

- Kostenbeperkingen, vooral voor hoogvolume consumententoepassingen

- Specifieke toepassingsvereisten, zoals bedrijfsomgeving en betrouwbaarheidsnormen

- Toekomstige schaalbaarheid en integratiebehoeften voor het product of systeem

V5: Wat zijn de opkomende trends in chipverpakking voor de toekomst?

A5: Enkele van de opkomende trends in chipverpakking voor de toekomst zijn:

- Voortdurende miniaturisatie en verhoogde integratie door middel van geavanceerde verpakkingstechnieken zoals fan-out wafer level packaging (FOWLP) en 3D/2,5D verpakking.

- Gebruik van nieuwe en geavanceerde materialen voor substraten, inkapseling en oplossingen voor thermisch beheer om de prestaties en betrouwbaarheid te verbeteren.

- Ontwikkeling van inbeddingstechnologieën die passieve componenten zoals condensatoren en weerstanden integreren in de verpakking zelf, waardoor verdere miniaturisatie mogelijk wordt.

- Verkenning van heterogene integratie, waarbij verschillende soorten chips (bijv. logica, geheugen, analoog) in één pakket worden geïntegreerd voor verbeterde functionaliteit en prestaties.

- Meer aandacht voor oplossingen voor thermisch beheer, zoals vloeistofkoeling en geïntegreerde warmtespreiders, om de thermische uitdagingen van krachtige pakketten met veel vermogen aan te pakken.