Índice

PalancaIntroducción

Definición de envasado de chips

El empaquetado de chips es el proceso de encerrar y proteger un circuito integrado (CI) o chip semiconductor, proporcionándole un empaquetado seguro y duradero. Implica montar el chip en una carcasa protectora, establecer conexiones eléctricas y facilitar la disipación del calor generado durante el funcionamiento.

Importancia del embalaje de chips

El envasado de chips desempeña un papel crucial en la industria de los semiconductores, ya que garantiza el buen funcionamiento, la fiabilidad y la durabilidad de los dispositivos electrónicos. Protege el delicado chip de factores externos como la humedad, el polvo y la tensión mecánica, al tiempo que permite unas conexiones eléctricas y una gestión térmica eficientes.

Tipos de métodos de empaquetado de chips

Embalaje Leadframe

El envasado en leadframe es uno de los métodos más comunes y tradicionales de envasado de chips. Consiste en montar el chip en un leadframe metálico, que proporciona conexiones eléctricas y soporte.

Encapsulado de plástico doble en línea (PDIP)

El encapsulado PDIP (Plastic Dual In-line Package) es un encapsulado de orificio pasante con dos filas paralelas de conductores. Se utiliza ampliamente en diversos dispositivos electrónicos, como ordenadores, electrónica de consumo y dispositivos de almacenamiento. aplicaciones industriales.

Circuito integrado de contorno pequeño (SOIC)

El circuito integrado de contorno pequeño (SOIC) es un encapsulado de montaje en superficie que presenta conductores en forma de ala de gaviota. Tiene un tamaño compacto y se utiliza habitualmente en teléfonos inteligentes, ordenadores portátiles y otros dispositivos electrónicos portátiles.

Matriz de bolas (BGA)

El Ball Grid Array (BGA) es una técnica de embalaje de montaje en superficie que utiliza una matriz de bolas de soldadura como conexiones eléctricas. Ofrece un elevado número de pines y es adecuada para aplicaciones de alta densidad y alto rendimiento.

Matriz de bolas de plástico (PBGA)

En Rejilla de bolas de plástico (PBGA) es una variante económica del encapsulado BGA, con un sustrato de plástico y bolas de soldadura para las conexiones eléctricas. Se utiliza mucho en electrónica de consumo y periféricos informáticos.

Matriz de bolas de cerámica (CBGA)

En Rejilla de bolas de cerámica (CBGA) es un encapsulado fiable y de alto rendimiento adecuado para entornos difíciles. Incorpora un sustrato cerámico y se utiliza habitualmente en aplicaciones militares, aeroespaciales e industriales.

Flip Chip

El embalaje flip chip es una técnica en la que el chip se monta boca abajo sobre el sustrato o el soporte del embalaje. Este método proporciona un tamaño de envase compacto y un mejor rendimiento eléctrico gracias a las conexiones más cortas entre el chip y el sustrato.

Embalaje a nivel de oblea (WLP)

Embalaje a nivel de oblea (WLP) es un método de envasado avanzado que consiste en envasar los chips mientras aún están en forma de oblea, antes de que sean singulados (cortados en chips individuales).

Embalaje Fan-Out a nivel de oblea (FOWLP)

El Fan-Out Wafer Level Packaging (FOWLP) es una variante del WLP en la que el encapsulado es mayor que el propio chip. Esto permite una mayor densidad de entrada/salida (E/S) y una mayor integración.

Embalaje Fan-In a nivel de oblea (FIWLP)

El Fan-In Wafer Level Packaging (FIWLP) es otro tipo de WLP en el que el tamaño del envase es inferior o igual al tamaño del chip. Ofrece un factor de forma compacto y es adecuado para dispositivos móviles y portátiles.

Factores que influyen en la selección del encapsulado de chips

Tamaño y factor de forma

El tamaño y el factor de forma del dispositivo electrónico son factores cruciales a la hora de seleccionar el método de empaquetado de chips adecuado. Los encapsulados compactos como BGA y WLP son preferibles para aplicaciones portátiles y con limitaciones de espacio, mientras que los encapsulados más grandes como PDIP pueden ser adecuados para aplicaciones de sobremesa o industriales.

Gestión térmica

Una gestión térmica eficaz es esencial para garantizar el funcionamiento fiable de los chips. Para las aplicaciones de alta potencia y alto rendimiento se prefieren los métodos de envasado que ofrecen una buena capacidad de disipación del calor, como los envases cerámicos o los envases con disipadores de calor.

Rendimiento eléctrico

Los requisitos de rendimiento eléctrico, incluida la integridad de la señal, el suministro de energía y la compatibilidad electromagnética (CEM), influyen en la elección del encapsulado del chip. Los paquetes con trayectorias eléctricas más cortas y mejores capacidades de apantallamiento, como flip chip o BGA, ofrecen un rendimiento eléctrico superior.

Coste

El coste es un factor importante, sobre todo en electrónica de consumo y aplicaciones de gran volumen. Los encapsulados de plástico como PDIP, SOIC y PBGA suelen ser más rentables que los encapsulados cerámicos o las técnicas de encapsulado avanzadas como WLP.

Requisitos de solicitud

Los requisitos específicos de la aplicación de destino, como el entorno operativo, las normas de fiabilidad y las especificaciones de rendimiento, desempeñan un papel crucial en la selección del método de empaquetado de chips adecuado.

Proceso y materiales de envasado

Preparación del troquel

El proceso de envasado comienza con la preparación de la matriz semiconductora (chip). Esto implica el procesamiento de la oblea, las pruebas y la singulación (corte de la oblea en chips individuales).

Sustrato o Leadframe

El sustrato o leadframe proporciona la base para el chip y establece las conexiones eléctricas. Los materiales más comunes son el plástico, la cerámica y metales como el cobre o el aluminio.

Vinculación

El bonding es el proceso de crear conexiones eléctricas entre el chip y el sustrato o leadframe. Puede realizarse mediante wire bonding, flip chip bonding u otras técnicas.

Encapsulación

La encapsulación consiste en encerrar el chip y sus conexiones eléctricas en un material protector, como plástico o cerámica. Este paso protege el chip de factores externos y le proporciona soporte estructural.

Pruebas y marcado

Tras el encapsulado, el chip empaquetado se somete a pruebas exhaustivas para garantizar su funcionalidad y fiabilidad. A continuación, se marca con información identificativa, como números de pieza o logotipos del fabricante.

Tendencias y futuro del envasado de chips

Miniaturización y mayor integración

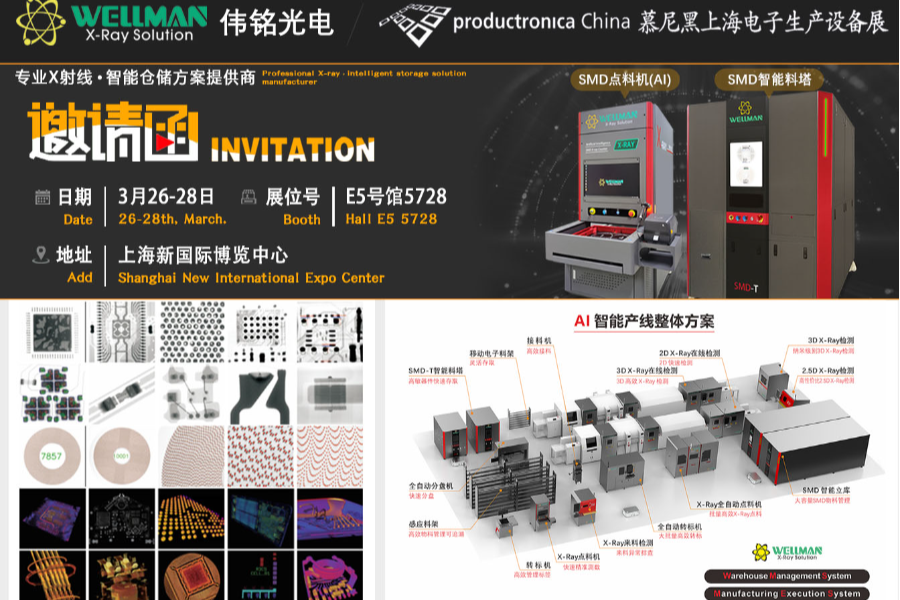

La tendencia a la miniaturización y a una mayor integración está impulsando el desarrollo de técnicas de envasado de chips más pequeños y compactos. Esto incluye la adopción de métodos de envasado avanzados como el WLP y el envasado 3D/2,5D.

Materiales avanzados

Se están estudiando materiales nuevos y avanzados para el encapsulado de chips con el fin de mejorar el rendimiento, la fiabilidad y la gestión térmica. Entre ellos figuran los sustratos orgánicos de alto rendimiento, las soluciones de refrigeración líquida y los materiales de encapsulado avanzados.

Envases 3D y 2,5D

Las tecnologías de envasado 3D y 2,5D, que consisten en apilar varios chips o integrar chips y componentes pasivos en un único envase, están ganando adeptos. Estas técnicas ofrecen mayor integración, mejores prestaciones y factores de forma reducidos.

Conclusión

Los métodos de envasado de chips desempeñan un papel vital en la industria de semiconductores, ya que garantizan la protección, funcionalidad y fiabilidad de los dispositivos electrónicos. Desde los tradicionales encapsulados leadframe hasta técnicas avanzadas como el WLP y el encapsulado 3D, la selección del método de encapsulado adecuado depende de varios factores, como el tamaño, la gestión térmica, el rendimiento eléctrico, el coste y los requisitos de la aplicación.

A medida que la tecnología siga evolucionando, los métodos de empaquetado de chips tendrán que adaptarse para satisfacer las demandas de mayor integración, mejor rendimiento y factores de forma más compactos. El futuro del empaquetado de chips pasa por el desarrollo de materiales innovadores, técnicas avanzadas de empaquetado y esfuerzos continuos de miniaturización para satisfacer las crecientes necesidades de la industria electrónica.

preguntas frecuentes

P1: ¿Cuál es la diferencia entre el empaquetado de obleas fan-out y fan-in?

A1: En el empaquetado fan-out a nivel de oblea (FOWLP), el tamaño del paquete es mayor que el del propio chip, lo que permite una mayor densidad de entrada/salida (E/S) y una mayor integración. En cambio, el fan-in.

P2: ¿Cuáles son las ventajas de los envases BGA?

A2: Los envases de matriz de bolas (BGA) ofrecen varias ventajas, entre ellas:

- Gran número de pines y alta densidad: Los encapsulados BGA pueden alojar un gran número de conexiones de entrada/salida, lo que los hace idóneos para aplicaciones de alto rendimiento y alta densidad.

- Rendimiento eléctrico mejorado: Los trayectos eléctricos más cortos de los encapsulados BGA mejoran la integridad de la señal y reducen el ruido, lo que permite frecuencias de funcionamiento más altas.

- Gestión térmica mejorada: La matriz de bolas de soldadura proporciona una mayor superficie para la disipación del calor, lo que mejora el rendimiento térmico.

- Compatibilidad con el montaje en superficie: Los encapsulados BGA están diseñados para la tecnología de montaje en superficie, lo que permite automatizar los procesos de montaje y reducir los requisitos de espacio en la placa.

P3: ¿Para qué sirve el encapsulado en el envasado de chips?

A3: La encapsulación es un paso crucial en el empaquetado de chips que cumple varios propósitos:

- Protección: Protege el delicado chip y sus conexiones eléctricas de factores externos como la humedad, el polvo y el estrés mecánico, garantizando la fiabilidad y prolongando la vida útil del chip.

- Soporte estructural: El material de encapsulado, como el plástico o la cerámica, proporciona integridad estructural y robustez al envase, evitando daños durante su manipulación y funcionamiento.

- Gestión térmica: Algunos materiales de encapsulado poseen una buena conductividad térmica, lo que facilita la disipación del calor del chip.

- Aislamiento eléctrico: El material de encapsulado aísla eléctricamente el chip y sus conexiones de interferencias externas o cortocircuitos.

P4: ¿Cuáles son las consideraciones clave a la hora de seleccionar un método de empaquetado de chips?

A4: La selección de un método de empaquetado de chips depende de varias consideraciones clave:

- Requisitos de tamaño y factor de forma de la aplicación final

- Necesidades de gestión térmica basadas en la disipación de potencia del chip

- Requisitos de rendimiento eléctrico, como integridad de la señal y suministro de energía

- Limitaciones de costes, especialmente para aplicaciones de consumo de gran volumen.

- Requisitos específicos de la aplicación, como entorno operativo y normas de fiabilidad

- Escalabilidad futura y necesidades de integración del producto o sistema

P5: ¿Cuáles son las nuevas tendencias en el envasado de chips para el futuro?

A5: Algunas de las tendencias emergentes en el envasado de chips para el futuro incluyen:

- Continuación de la miniaturización y aumento de la integración mediante técnicas de envasado avanzadas como el envasado de obleas en abanico (FOWLP) y el envasado 3D/2,5D.

- Adopción de materiales nuevos y avanzados para sustratos, encapsulación y soluciones de gestión térmica para mejorar el rendimiento y la fiabilidad.

- Desarrollo de tecnologías de incrustación que integran componentes pasivos como condensadores y resistencias en el propio envase, lo que permite una mayor miniaturización.

- Exploración de la integración heterogénea, en la que distintos tipos de chips (por ejemplo, lógicos, de memoria, analógicos) se integran en un solo paquete para mejorar la funcionalidad y el rendimiento.

- Mayor atención a las soluciones de gestión térmica, como la refrigeración líquida y los dispersores de calor integrados, para afrontar los retos térmicos de los paquetes de alto rendimiento y gran densidad de potencia.