Indice dei contenuti

Alternaintroduzione

Definizione di imballaggio per chip

L'imballaggio dei chip è il processo di racchiudere e proteggere un circuito integrato (IC) o un chip a semiconduttore, fornendogli un pacchetto sicuro e durevole. Comporta l'assemblaggio del chip in un involucro protettivo, la creazione di connessioni elettriche e l'agevolazione della dissipazione del calore generato durante il funzionamento.

Importanza dell'imballaggio dei chip

L'imballaggio dei chip svolge un ruolo cruciale nell'industria dei semiconduttori, in quanto garantisce il corretto funzionamento, l'affidabilità e la durata dei dispositivi elettronici. Protegge il delicato chip da fattori esterni quali umidità, polvere e stress meccanico, consentendo al contempo connessioni elettriche e gestione termica efficienti.

Tipi di metodi di confezionamento dei chip

Imballaggio del leadframe

Il confezionamento leadframe è uno dei metodi più comuni e tradizionali di confezionamento dei chip. Consiste nel montare il chip su un leadframe metallico, che fornisce connessioni elettriche e supporto.

Pacchetto in plastica a doppia linea (PDIP)

Il package PDIP (Plastic Dual In-line Package) è un package a foro passante con due file parallele di conduttori. È ampiamente utilizzato in vari dispositivi elettronici, come computer, elettronica di consumo e dispositivi di controllo. applicazioni industriali.

Circuito integrato di piccole dimensioni (SOIC)

Lo Small Outline Integrated Circuit (SOIC) è un contenitore a montaggio superficiale che presenta conduttori a forma di ali di gabbiano. Offre dimensioni compatte ed è comunemente utilizzato in smartphone, laptop e altri dispositivi elettronici portatili.

Griglia a sfere (BGA)

Il Ball Grid Array (BGA) è una tecnica di confezionamento a montaggio superficiale che utilizza un array di sfere di saldatura come connessioni elettriche. Offre un elevato numero di pin ed è adatta ad applicazioni ad alta densità e ad alte prestazioni.

Griglia di sfere in plastica (PBGA)

Il Griglia di sfere in plastica (PBGA) è una variante economica del pacchetto BGA, con un substrato di plastica e sfere di saldatura per le connessioni elettriche. È ampiamente utilizzato nell'elettronica di consumo e nelle periferiche per computer.

Griglia a sfere in ceramica (CBGA)

Il Griglia di sfere in ceramica (CBGA) è un pacchetto affidabile e ad alte prestazioni, adatto ad ambienti difficili. È dotato di un substrato in ceramica ed è comunemente utilizzato in applicazioni militari, aerospaziali e industriali.

Flip Chip

Il confezionamento Flip Chip è una tecnica in cui il chip è montato a faccia in giù sul substrato o sul supporto della confezione. Questo metodo consente di ottenere un pacchetto di dimensioni compatte e di migliorare le prestazioni elettriche grazie alle connessioni più corte tra il chip e il substrato.

Imballaggio a livello di wafer (WLP)

Imballaggio a livello di wafer (WLP) è un metodo di confezionamento avanzato che prevede l'imballaggio dei chip quando sono ancora in forma di wafer, prima che vengano singolarizzati (tagliati in singoli chip).

Imballaggio a livello di wafer con uscita a ventaglio (FOWLP)

Il Fan-Out Wafer Level Packaging (FOWLP) è una variante del WLP in cui il package è più grande del chip stesso. Ciò consente una maggiore densità di input/output (I/O) e una maggiore integrazione.

Imballaggio a livello di wafer Fan-In (FIWLP)

Il Fan-In Wafer Level Packaging (FIWLP) è un altro tipo di WLP in cui le dimensioni del pacchetto sono inferiori o uguali a quelle del chip. Offre un fattore di forma compatto ed è adatto ai dispositivi mobili e indossabili.

Fattori che influenzano la scelta dell'imballaggio dei chip

Dimensioni e fattore di forma

Le dimensioni e il fattore di forma del dispositivo elettronico sono fattori cruciali nella scelta del metodo di confezionamento dei chip più adatto. I package compatti, come BGA e WLP, sono preferiti per le applicazioni portatili e con limiti di spazio, mentre i package più grandi, come i PDIP, possono essere adatti per le applicazioni desktop o industriali.

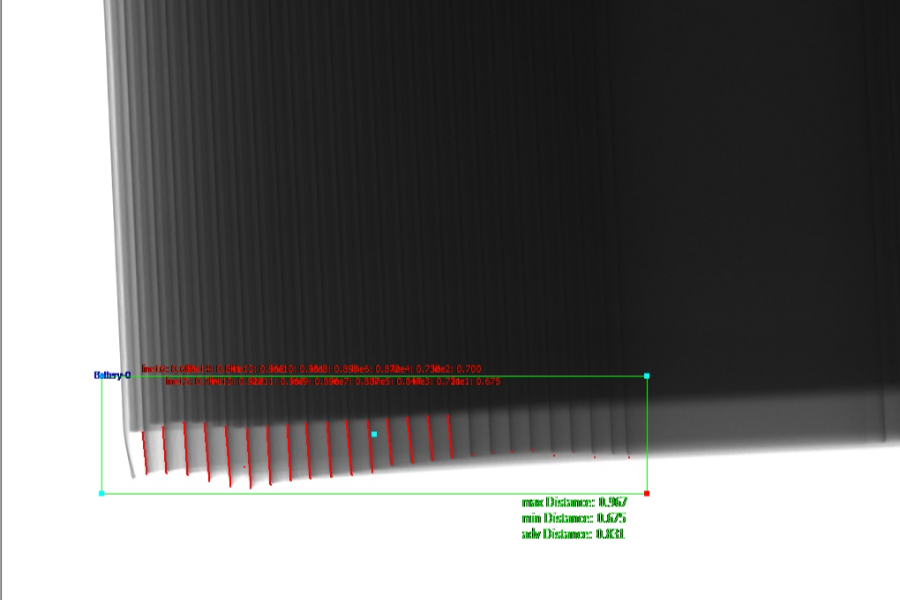

Gestione termica

Una gestione termica efficace è essenziale per garantire il funzionamento affidabile dei chip. I metodi di confezionamento che offrono buone capacità di dissipazione del calore, come i pacchetti ceramici o i pacchetti con diffusori di calore, sono preferiti per le applicazioni ad alta potenza e ad alte prestazioni.

Prestazioni elettriche

I requisiti di prestazione elettrica, tra cui l'integrità del segnale, l'erogazione di potenza e la compatibilità elettromagnetica (EMC), influenzano la scelta del packaging del chip. I pacchetti con percorsi elettrici più brevi e migliori capacità di schermatura, come i flip chip o i BGA, offrono prestazioni elettriche superiori.

Costo

Il costo è un fattore importante, soprattutto nell'elettronica di consumo e nelle applicazioni ad alto volume. I package in plastica, come PDIP, SOIC e PBGA, sono generalmente più convenienti rispetto ai package in ceramica o alle tecniche di packaging avanzate come il WLP.

Requisiti per l'applicazione

I requisiti specifici dell'applicazione di destinazione, come l'ambiente operativo, gli standard di affidabilità e le specifiche di prestazione, svolgono un ruolo fondamentale nella scelta del metodo di confezionamento dei chip più adatto.

Processo e materiali di imballaggio

Preparazione degli stampi

Il processo di confezionamento inizia con la preparazione della matrice del semiconduttore (chip). Ciò comporta la lavorazione del wafer, il test e la singolazione (taglio del wafer in singoli chip).

Substrato o struttura portante

Il substrato o leadframe costituisce la base per il chip e stabilisce le connessioni elettriche. I materiali comunemente utilizzati sono plastica, ceramica e metalli come rame o alluminio.

Legame

Il bonding è il processo di creazione di connessioni elettriche tra il chip e il substrato o il leadframe. Questo processo può essere realizzato attraverso il wire bonding, il flip chip bonding o altre tecniche.

Incapsulamento

L'incapsulamento consiste nel racchiudere il chip e le sue connessioni elettriche in un materiale protettivo, come la plastica o la ceramica. Questa fase protegge il chip da fattori esterni e fornisce un supporto strutturale.

Test e marcatura

Dopo l'incapsulamento, il chip confezionato viene sottoposto a test approfonditi per garantirne la funzionalità e l'affidabilità. Viene quindi contrassegnato con informazioni di identificazione, come numeri di parte o loghi del produttore.

Tendenze e futuro dell'imballaggio dei chip

Miniaturizzazione e maggiore integrazione

La tendenza alla miniaturizzazione e alla maggiore integrazione sta spingendo lo sviluppo di tecniche di confezionamento dei chip più piccole e compatte. Ciò include l'adozione di metodi di confezionamento avanzati come il WLP e il confezionamento 3D/2.5D.

Materiali avanzati

Per il packaging dei chip si stanno studiando materiali nuovi e avanzati per migliorare le prestazioni, l'affidabilità e la gestione termica. Questi includono substrati organici ad alte prestazioni, soluzioni di raffreddamento a liquido e materiali di incapsulamento avanzati.

Imballaggio 3D e 2,5D

Le tecnologie di packaging 3D e 2,5D, che prevedono l'impilamento di più chip o l'integrazione di chip e componenti passivi in un unico pacchetto, stanno guadagnando terreno. Queste tecniche offrono una maggiore integrazione, migliori prestazioni e fattori di forma ridotti.

Conclusione

I metodi di confezionamento dei chip svolgono un ruolo fondamentale nell'industria dei semiconduttori, garantendo la protezione, la funzionalità e l'affidabilità dei dispositivi elettronici. Dalle tradizionali confezioni leadframe alle tecniche avanzate come il WLP e il packaging 3D, la scelta del metodo di confezionamento appropriato dipende da vari fattori, tra cui le dimensioni, la gestione termica, le prestazioni elettriche, i costi e i requisiti applicativi.

Con la continua evoluzione della tecnologia, i metodi di confezionamento dei chip dovranno adattarsi per soddisfare le richieste di maggiore integrazione, migliori prestazioni e fattori di forma più compatti. Il futuro del confezionamento dei chip risiede nello sviluppo di materiali innovativi, di tecniche di confezionamento avanzate e di continui sforzi di miniaturizzazione per supportare le esigenze sempre crescenti dell'industria elettronica.

Domande frequenti

D1: Qual è la differenza tra il confezionamento a livello di wafer fan-out e fan-in?

A1: Nel fan-out wafer level packaging (FOWLP), le dimensioni del package sono maggiori del chip stesso, consentendo una maggiore densità di input/output (I/O) e una maggiore integrazione. D'altra parte, il fan-in.

D2: Quali sono i vantaggi del confezionamento ball grid array (BGA)?

A2: Il confezionamento BGA (Ball Grid Array) offre diversi vantaggi, tra cui:

- Alto numero di pin e alta densità: I pacchetti BGA possono ospitare un gran numero di connessioni di ingresso/uscita, rendendoli adatti ad applicazioni ad alte prestazioni e ad alta densità.

- Migliori prestazioni elettriche: I percorsi elettrici più brevi nei pacchetti BGA consentono una migliore integrità del segnale e una riduzione del rumore, consentendo frequenze operative più elevate.

- Gestione termica migliorata: L'array di sfere di saldatura offre una superficie maggiore per la dissipazione del calore, migliorando le prestazioni termiche.

- Compatibilità con il montaggio in superficie: I pacchetti BGA sono progettati per la tecnologia di montaggio superficiale, consentendo processi di assemblaggio automatizzati e riducendo i requisiti di spazio sulla scheda.

D3: Qual è lo scopo dell'incapsulamento nel confezionamento dei chip?

A3: L'incapsulamento è una fase cruciale del confezionamento dei chip che ha diversi scopi:

- Protezione: Protegge il delicato chip e le sue connessioni elettriche da fattori esterni come umidità, polvere e stress meccanico, garantendo l'affidabilità e prolungando la durata del chip.

- Supporto strutturale: Il materiale di incapsulamento, come la plastica o la ceramica, garantisce l'integrità strutturale e la robustezza del pacchetto, evitando danni durante la manipolazione e il funzionamento.

- Gestione termica: Alcuni materiali di incapsulamento possiedono una buona conducibilità termica, facilitando la dissipazione del calore dal chip.

- Isolamento elettrico: Il materiale di incapsulamento isola elettricamente il chip e le sue connessioni da interferenze esterne o cortocircuiti.

D4: Quali sono le considerazioni principali nella scelta di un metodo di confezionamento dei chip?

A4: La scelta di un metodo di confezionamento dei chip dipende da diverse considerazioni chiave:

- Requisiti di dimensione e fattore di forma dell'applicazione finale

- Esigenze di gestione termica basate sulla dissipazione di potenza del chip

- Requisiti di prestazione elettrica, come l'integrità del segnale e l'erogazione di potenza

- Vincoli di costo, in particolare per le applicazioni di consumo ad alto volume

- Requisiti specifici dell'applicazione, come l'ambiente operativo e gli standard di affidabilità

- Esigenze future di scalabilità e integrazione del prodotto o del sistema

D5: Quali sono le tendenze emergenti nel packaging dei chip per il futuro?

A5: Alcune delle tendenze emergenti nel packaging dei chip per il futuro includono:

- Continua miniaturizzazione e maggiore integrazione grazie a tecniche di packaging avanzate come il fan-out wafer level packaging (FOWLP) e il packaging 3D/2.5D.

- Adozione di materiali nuovi e avanzati per substrati, incapsulamento e soluzioni di gestione termica per migliorare le prestazioni e l'affidabilità.

- Sviluppo di tecnologie di incorporazione che integrano componenti passivi come condensatori e resistenze nella confezione stessa, consentendo un'ulteriore miniaturizzazione.

- Esplorazione dell'integrazione eterogenea, in cui diversi tipi di chip (ad esempio, logici, di memoria, analogici) sono integrati in un unico pacchetto per migliorare funzionalità e prestazioni.

- Maggiore attenzione alle soluzioni di gestione termica, come il raffreddamento a liquido e i diffusori di calore integrati, per affrontare le sfide termiche dei pacchetti ad alte prestazioni e ad alta densità di potenza.